# 256Mb NAND FLASH

**AFND5608S1**

| Revision No. | History       | Draft Date | Remark      |

|--------------|---------------|------------|-------------|

| Rev.00       | Initial Draft | Nov. 2011  | Preliminary |

#### **FEATURES SUMMARY**

### Power Supply

-1.8V Device(AFND5608S1) 1.7V ~ 1.95V

### Organization

-Memory Cell Array : (32M + 1024K) x 8bits

-Data Register: (512 + 16) x 8bits

### Automatic Program and Erase

-Page Program : (512 + 16)Bytes -Block Erase : (16K +512)Bytes

### • Page Read Operation

-Page Size: (512 + 16)Bytes-Random Access: 15us(Max.)-Serial Page Access: 50ns(Min.)

### • Fast Write Cycle Time

-Program time : 200us(Typ.) -Block Erase time : 2ms(Typ.)

### • Copy-Back PROGRAM Operation

-Fast Page copy without external buffering

### Command Register Operation

### Security features

-OTP area, 16Kbytes(32 pages)

#### Hardware Data Protection

-Program / Erase locked during Power transitions

### Data Integrity

-Endurance: 100K Program / Erase Cycles

(With 1bit/528byte ECC) -Data Retention : 10 years

#### Package

-AFND5608S1 : Pb-Free Package 48-pin TSOP(12 x 20 / 0.5 mm pitch) 48-Ball FBGA: 9.0 x 9.0 x 1.0mm

#### **GENERAL DESCRIPTION**

The AFND5608S1 is 256Mbit with spare 8Mbit capacity. The device is offered in 1.8V power supply. Its NAND cell provides the most cost-effective solution for the solid state mass storage market. A program operation can be performed in typical 200us on the 528-bytes and an erase operation can be performed in typical 2ms on a 16K-bytes block. Data in the page can be read out at 50ns cycle time per byte. The I/O pins serve as the ports for address and data input/output as well as command input. Command, Data and Address are synchronously introduced using /CE, /WE, ALE and CLE input pin. The output pin R/B(open drain buffer) signals the status of the device during each operation. In a system with multiple memories the R/B pins can be connected all together to provide a global status signal. The on-chip write control automates all program and erase functions including pulse repetition, where required, and internal verification and margining of data. Even the write-intensive systems can take advantage of the AFND5608S1's extended reliability of 100K program / erase cycles by providing ECC(Error Correction Code) with real time mapping-out algorithm.

The chip could be offered with the /CE don't care function. This function allows the direct download of the code form the NAND flash memory device by a microcontroller, since the /CE transitions do not stop the read operation.

The copy back function allows the optimization of defective blocks management: when a page program operation fails the data can be directly programmed in another page inside the same array section without the time consuming serial data insertion phase. Also, this device includes extra features like OTP area.

The AFND5608S1 is an optimum solution for large nonvolatile storage applications such as solid state file storage and other portable applications requiring non-volatility.

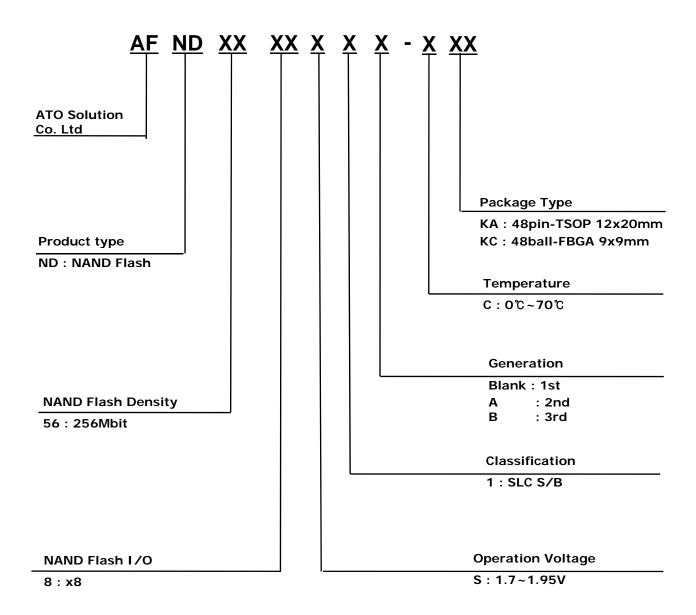

### **Ordering Information**

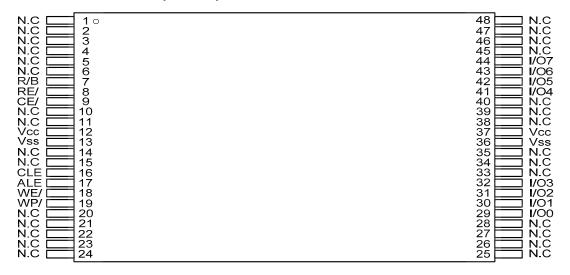

### PIN CONFIGURATION (TSOP1)

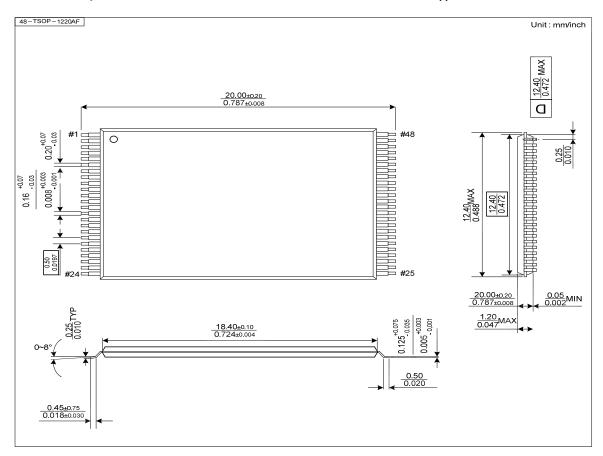

#### PACKAGE DIMENSIONS

48-PIN LEAD/LEAD FREE PLASTIC THIN SMALL OUT-LINE PACKAGE TYPE(I)

## PIN CONFIGURATION (48ball-FBGA )

|   | 1   | 2     | 3     | 4   | 5     | 6   |

|---|-----|-------|-------|-----|-------|-----|

| A | WP# | ALE   | VSS   | CE# | WE#   | R/B |

| В | NC  | RE#   | CLE   | NC  | NC    | NC  |

| С | NC  | NC    | NC    | NC  | NC    | NC  |

| D | NC  | NC    | NC    | NC  | NC    | NC  |

| Е | NC  | NC    | NC    | NC  | NC    | NC  |

| F | NC  | 100   | NC    | NC  | NC    | VCC |

| G | NC  | (IO1) | NC    | VCC | 105   | 107 |

| Н | VSS | lO2   | (103) | lO4 | (106) | VSS |

|   |     |       |       |     |       |     |

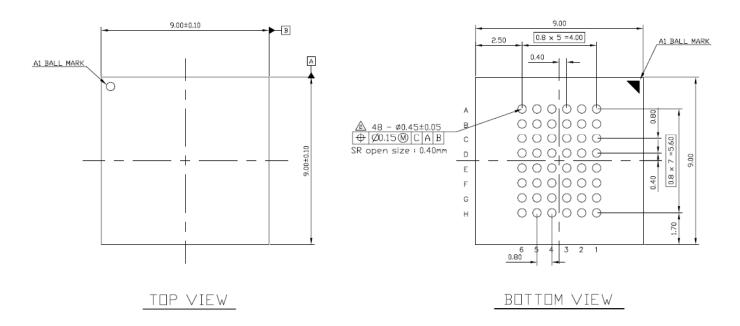

### PACKAGE OUTLINE DRAWING (48ball-FBGA 9x9mm)

- 1. ALL DIMENSIONS are in Millimeters.

- POST REFLOW SOLDER BALL DIAMETER.

(Pre Reflow diameter : Ø0.40±0.02)

### PIN DESCRIPTION

| Pin<br>Name    | Pin Function                                                                                                                                                                                                                                                                                                                               |  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| I/O0 ~<br>I/O7 | DATA INPUTS/OUTPUTS  The I/O pins are used to input command, address and data, and to output data during read operations. The I/O pins float to high-z when the chip is deselected or when the outputs are disabled.                                                                                                                       |  |  |  |

| CLE            | COMMAND LATCH ENABLE The CLE input controls the activating path for commands sent to the command register. When active high, commands are latched into the command register through the I/O ports on the rising edge of the /WE signal.                                                                                                    |  |  |  |

| ALE            | ADDRESS LATCH ENABLE The ALE input controls the activating path for address to the internal address registers. Addresses are latched on the rising edge of /WE with ALE high                                                                                                                                                               |  |  |  |

| /CE            | CHIP ENABLE The /CE input is the device selection control. When the device is in the Busy state, /CE high is ignored, and the device does not return to standby mode in program or erase operation. Regarding /CE control during read operation, refer to 'Page Read' section of device operation.                                         |  |  |  |

| /RE            | READ ENABLE The /RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of /RE which also increments the internal column address counter by one.                                                                                                             |  |  |  |

| /WE            | WRITE ENABLE The /WE input controls writes to the I/O port. Commands, address and data are latched on the rising edge of the /WE pulse.                                                                                                                                                                                                    |  |  |  |

| /WP            | WRITE PROTECT The /WP pin provides inadvertent write/erase protection during power transitions. The internal high voltage generator is reset when the /WP pin is active low.                                                                                                                                                               |  |  |  |

| R/B            | READY/BUSY OUTPUT  The R/B output indicates the status of the device operation. When low, it indicates that a program, erase of random read operation is in process and returns to high state upon completion. It is an open drain output and does not float to high-z condition when the chip is deselected or when outputs are disabled. |  |  |  |

| Vcc            | POWER Vcc is the power supply for device.                                                                                                                                                                                                                                                                                                  |  |  |  |

| Vss            | GROUND                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| N.C            | NO CONNECTION Lead is not internally connected.                                                                                                                                                                                                                                                                                            |  |  |  |

Note: Connect all Vcc and Vss pins of each device to common power supply outputs Do not leave Vcc or Vss disconnected.

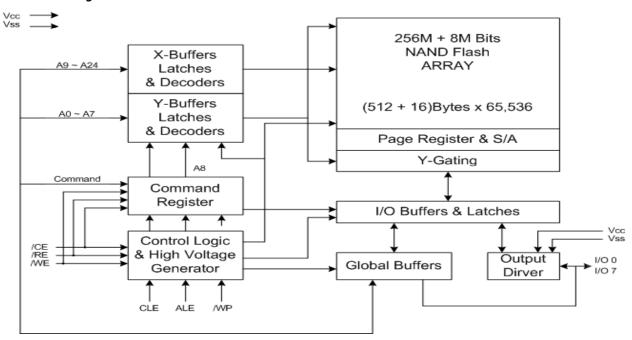

Figure 1. AFND5608S1 FUNCTIONAL BLOCK DIAGRAM

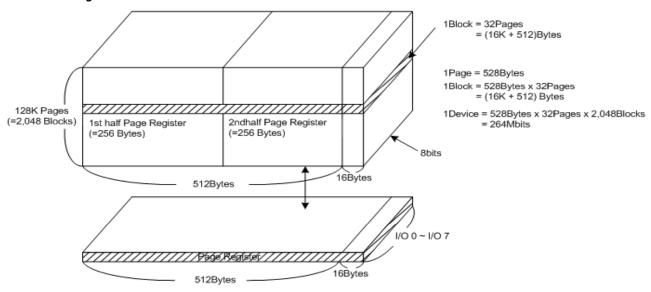

Figure 2. AFND5608S1 ARRAY ORGANIZATION

| ſ |           | I/O 0 | 1/0 0 |

|---|-----------|-------|-------|-------|-------|-------|-------|-------|-------|

|   | 1st Cycle | A0    | A1    | A2    | A3    | A4    | A5    | A6    | A7    |

|   | 2nd Cycle | A9    | A10   | A11   | A12   | A13   | A14   | A15   | A16   |

| Γ | 3rd Cycle | A17   | A18   | A19   | A20   | A21   | A22   | A23   | A24   |

Column Address Row Address (Page Address)

NOTE: Column Address: Starting Address of the Register.

00h Command(Read) : Defines the starting address of the 1st half of the register. 01h Command(Read) : Defines the starting address of the 2nd half of the register.

\* A8 is set to "Low" or "High" by the 00h or 01h Command.

<sup>\*</sup> The device ignores any additional input of address cycles than required.